JAN Issue 1/2010 www.edn.com

Premier Farnell's Marianne Culver Pg 54

E-readers and obsolescence Pg 4

It's a Gaussian world Pg 14

MEMS, sensors, and nanotechnology Pg 16

Design Ideas Pg 43

Tales from the Cube Pg 60

## **UNDER THE LID**

ANALOG TEST IS SUDDENLY THE CRITICAL INGREDIENT Page 24

## INNOVATIVE PACKAGING

IMPROVES LEDS' LIGHT OUTPUT, LIFETIME, AND RELIABILITY

Page 21

## **ANECHOIC CHAMBERS**

RISE FROM THE PITS

Page 31

## **CONGESTION MANAGEMENT**

CLEARS A PATH THROUGH 10 GbE

Page 37

Product Innovation from Cirrus Logic

## DP 12-PIN POWER SIP

(actual footprint 30.99mm X 20.17mm)

## FC MODULAR 42-PIN DIP

Open Frame Product Technology (actual footprint 65.1mm X 42.5mm)

## **NORTH AMERICA**

+1 800-625-4084

### ASIA PACIFIC

+852 2376-0801

## JAPAN

+81 (3) 5226-7757

## EUROPE/UK

+44 (0) 1628-891-300

# Piezoelectric actuator Ref1 + 200V Piezoelectric actuator -200V -200V

## Dual Channel Amplifier is a Space Saver For Piezoelectric Actuator Drives

The MP103FC is a dual channel power amplifier that sets new standards for combining high current, high speed and high voltage for the Apex Precision Power® family of linear amplifiers from Cirrus Logic. The MP103FC has a power bandwidth rated at 230 kHz, and a 180 V/µs slew rate, for driving piezo electric applications that require lower speeds but multiple drivers. The device also features up to 15 A of output current per channel and an operating voltage ranging from

30 V up to 200 V. The MP103FC uses "open frame" modular packaging that is ideal for high speed assembly and provides a low per unit cost in comparison with many in-house discrete designs.

| Model   | Slew<br>Rate | Output<br>Current            | Supply Voltage<br>Operation  |

|---------|--------------|------------------------------|------------------------------|

| MP103FC | 180 V/µs     | Up To<br>15 A PEAK           | 30 V to 200 V<br>Dual Supply |

| PA107DP | 3000 V/μs    | 1.5 A continuous<br>5 A Peak | 40 V to 200 V<br>Dual Supply |

THE CIRRUS LOGIC V15 APEX

PRECISION POWER PRODUCT

DATA BOOK IS HERE! REQUEST

YOUR FREE COPY, OR DOWNLOAD

AT WWW.CIRRUS.COM/EDN100107

For product selection assistance or technical support with Apex Precision Power products call 1-800-546-2739 or apex.support@cirrus.com.

#1 Breadth of Product Line #1 Availability of Product #1 Overall Performance

Source: **EE**Times Distribution Study, August 2009

The industry's broadest product selection available for immediate delivery

www.digikey.com 1.800.344.4539

## EDN 1.7.10 contents

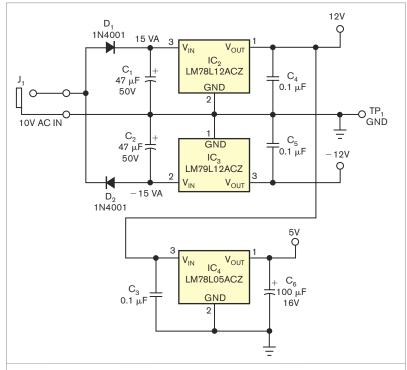

## Under the lid: Analog test is suddenly the critical ingredient

After years of attention to digital-test technology, analog test is emerging as a roadblock to cost reduction.

by Ron Wilson, Executive Editor

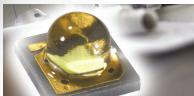

## Innovative packaging improves LEDs' light output, lifetime, and reliability

2 1 HB-LED packaging design continues to advance, contributing almost as much to performance as the LED chip itself.

by Margery Conner,

Technical Editor

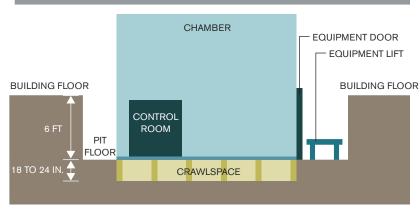

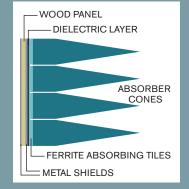

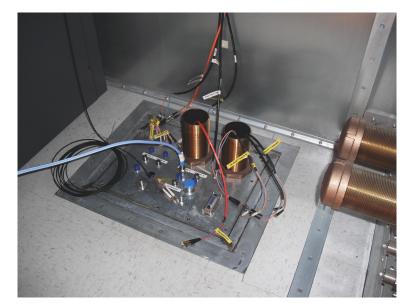

## Anechoic chambers rise from the pits

The design, construction, and qualification of a chamber depend on the products it will test. by Martin Rowe, Senior Technical Editor, Test & Measurement World

- 8 32-bit processor pushes deeper into 8-bit territory

- 8 ICs tackle accuracy in multiphase-metering applications

- 9 Chip provides speedy MPEG transcoding, trans-scaling

- 10 16-bit, dual-channel ADCs span 20M to 80M samples/ sec

- 11 Touchscreen controller provides tactile feedback

- 12 Analog FastSpice RF delivers noise analysis for RF circuits

- 12 Function-level visibility improves application optimizer

- 13 Research Update: Microants act as tiny conveyor belts inside chips; Biochip-based test aims at speedy disease diagnosis

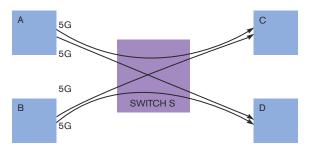

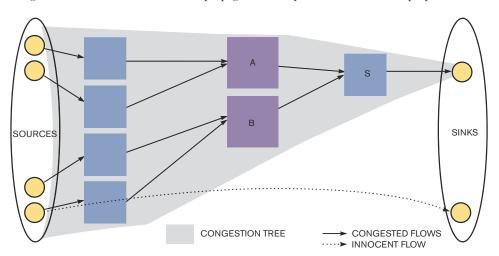

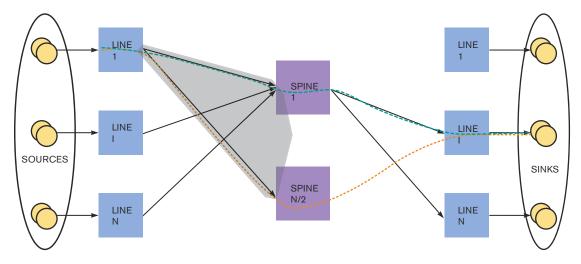

## Congestion management clears a path through 10 GbE

37 With the new IEEE standards for consolidation and the ability to build highly scalable high-speed Ethernet networks, Ethernet will become the only fabric you need for converged data centers, and it will lower the cost of supercomputer networks.

by Zhi-Hern Loh, Fulcrum Microsystems

## DESIGNIDEAS

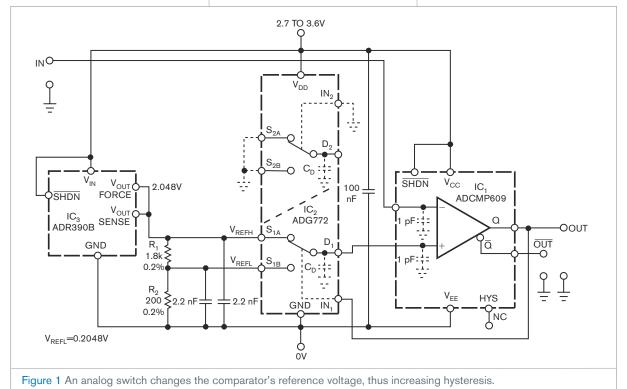

- 43 Circuit uses two reference voltages to improve hysteresis accuracy

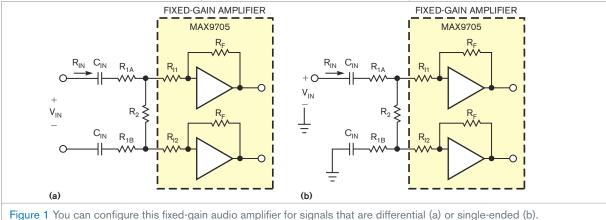

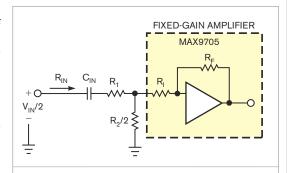

- 44 Resistor network sets gain for fixed-gain differential amplifier

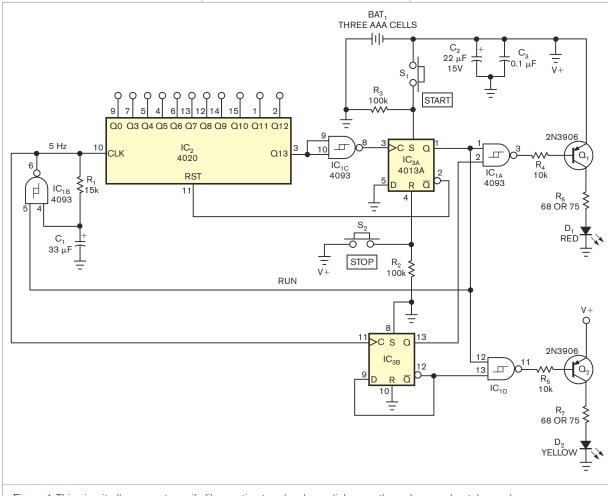

- 45 LED flasher checks fiber-optic strands

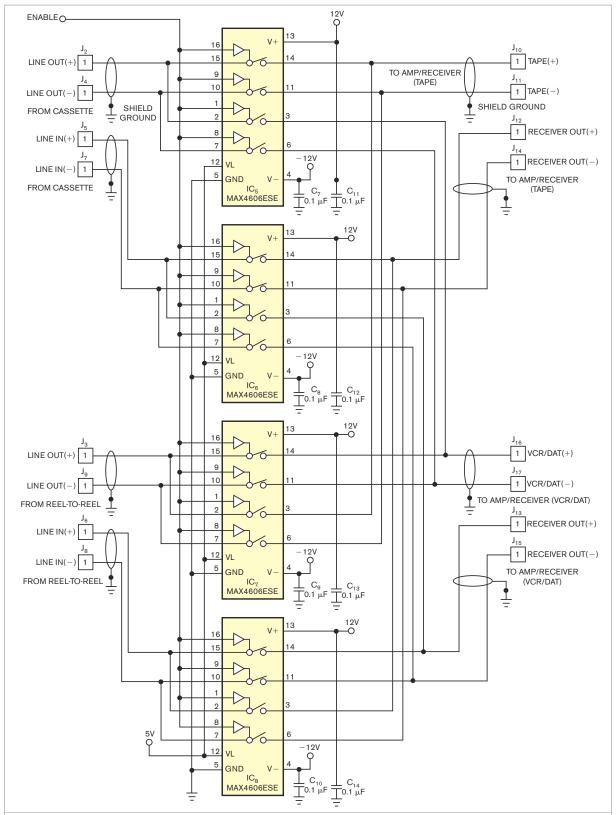

- 46 Circuit routes audio signals between equipment

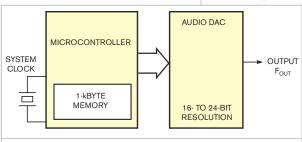

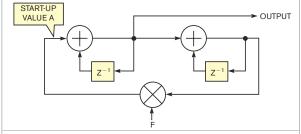

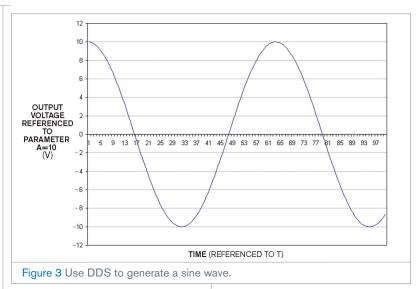

- 50 Microcontroller provides an alternative to DDS

## **DEPARTMENTS & COLUMNS**

- 4 EDN.comment: E-readers and obsolescence

- 14 Signal Integrity: It's a Gaussian world

- 16 Inside Nanotechnology: MEMS, sensors, and nanotechnology

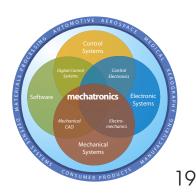

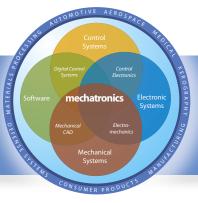

- 19 **Mechatronics in Design:** What's your point of view?

This new column, a joint effort among EDN and three of its sister publications, offers fresh ideas on integrating mechanical systems, electronics, control systems, and software in design.

- **Supply Chain:** Distributor taps CAD to meet designer needs; More possible changes to ROHS; Multicore mobile processors shipments on rise

- **Product Roundup:** Discrete Semiconductors, Computers and Peripherals, Integrated Components

- 60 Tales from the Cube: The nose knows

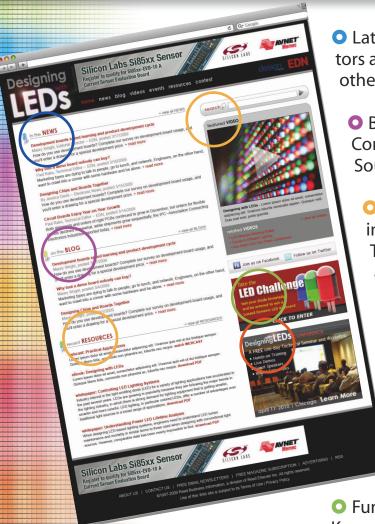

## **EDN**) online contents

www.edn.com

## ONLINE ONLY

Check out these Web-exclusive articles:

## Clock gating: Smart use ensures smart returns

Clock gating is a must-have technique for managing power, but errors in the design process can cause trouble later on.

→www.edn.com/article/CA6709780

## Mobile video quality: the new mediagateway revolution

Customer-defined applications are now driving telecommunications-product and -service offerings. Video telephony is a case in point, and mobile video is not far behind. Key success factors for video gateways are the quality of experience, ease of use, and affordability.

→www.edn.com/article/CA6711225

## **ENGINEERS' TRUE STORIES**

In EDNs Tales from the Cube, engineers relate their most vexing design challenges—and how they conquered them.

Here are some examples of how your peers solved real-world problems:

## Tanks a lot!

- →www.edn.com/article/CA6709576

- Keep on truckin'

- → www.edn.com/article/CA6702292

## The boss is always right, even when he's wrong

→www.edn.com/article/CA6662649

Read more in the Tales archive at www.edn.com/tales.

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, CEO/CFO, RBI-US, Jeff DeBalko, President, Business Media; Jane Volland, Vice President, Finance. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2010 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$1739.99 one year; Canada, \$229.99 one year (includes 7% GST, GST#123397457); Mexico, \$292.99 one year; air expedited, \$3299.99 one year Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6NA. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 55 Number 1 (Printed in USA).

## Simpler Power Conversion

IR's AC-DC product portfolio offers simple, compact high density solutions tailored for energy-efficient power supplies.

## µPFC™ PFC IC

| Part<br>Number     | Pckg.         | V <sub>cc</sub> (V) | Freq.<br>(kHz) | Gate<br>Drive<br>±(A) | V <sub>GATE</sub><br>Clamp<br>(V) | Current<br>Mode |

|--------------------|---------------|---------------------|----------------|-----------------------|-----------------------------------|-----------------|

| IR1150<br>(STR)PbF | SO-8<br>PDIP8 | 13-22               | 50-200         | 1.5                   |                                   | ССМ             |

## SmartRectifier™ IC

| Part<br>Number                 | IR1166S<br>PbF     | IR1167AS<br>PbF | IR1167BS<br>PbF | IR1168S<br>PbF |

|--------------------------------|--------------------|-----------------|-----------------|----------------|

| Package                        |                    |                 |                 |                |

| V <sub>cc</sub> (V)            | 20<br><=200        |                 |                 |                |

| V <sub>FET</sub> (V)           |                    |                 |                 |                |

| Sw Freq.<br>max (kHz)          | 500                |                 |                 |                |

| Gate Drive<br>±(A)             | +1/-4              | +2/-7           |                 | +1/-4          |

| V <sub>GATE</sub> Clamp<br>(V) | 10.7               | 10.7            | 14.5            | 10.7           |

| Min. On Time<br>(ns)           | Program. 250 -3000 |                 |                 | 750            |

| Channel                        | 1                  |                 |                 | 2              |

| RoHS                           | V                  |                 | V               | ~              |

For more information call 1.800.981.8699 or visit

www.irf.com

International Rectifier

THE POWER MANAGEMENT LEADER

## BY RICK NELSON, EDITOR-IN-CHIEF

## E-readers and obsolescence

arly adopters often get burned, but usually it's only on price, as I noted in a recent blog (Reference 1). As I remarked in the blog post, however, commenting on an article from *The Wall Street Journal*, e-readers could be the eight-track tapes of the 21st century (Reference 2). Various e-readers from different generations and different vendors may be incompatible, you can't easily lend an e-book to a friend, and an e-reader is an expensive piece of equipment to inadvertently leave behind somewhere.

The WSJ article quotes Bob LiVolsi, the founder of BooksOnBoard, as saying that dedicated e-readers are for people with disposable incomes who love technology—not books.

Book lovers might well settle for reading on a laptop or a netbook.

But most of those readers who commented on my blog strongly disagree. One mentions a preference for old-fashioned books but notes that laptops are battery hogs. One touts the adjustable font size as well as a user-friendly page-forward button that suits the device to an elderly parent. Many travelers cite the lightweight devices' ability to carry many books or stacks of data sheets.

One skeptical traveler points out that he would be dragging his laptop along anyway, suggesting that an ereader would be superfluous. And he's not about to replace his 1000-volume collection of real books with e-versions. But another commenter notes that laptops aren't that easy to use in coach seats. The general consensus

is that e-readers won't replace books but are a great addition, especially for travel.

The main criticism seems to be the need to continue buying the same content in different formats. EDN Senior Technical Editor Brian Dipert addresses this issue in his "Brian's Brain" blog (Reference 3). "Paintings and photographs may fade over time," he writes, "but if you've properly mounted and dis-

played them, you'll still be able to enjoy them for many decades. ... The same goes for film stock and magnetic-based magnetic tape for both audio and video, although you may need to supplement low-humidity and temperature-controlled archiving with an occasional oven bake. And the same goes for books, yellowed and tattered pages aside ... at least in the paper 'analog' generation."

Brian is now contending with being an early adopter of the first-generation Sony PRS-500 eBook read-

er. He explains, "Sony is transitioning its online eBook store from the proprietary BBeB [broadband-electronic-book format to industry-standard ePub [electronic publishing]. The firmware upgrade is necessary to add ePub support to the PRS-500. Curiously and for unknown reasons, a userinstallable firmware update utility is not available; PRS-500 owners need to send their units to Sony. To the company's credit, it's paying for the upgrade, including free and speedy ... round-trip shipping. And folks who've already shipped out their PRS-500s seem generally pleased with the process and outcome."

Brian continues, "But will my upgraded PRS-500 still be able to access the hundred-plus BBeB files stored on my SD [secure-digital] card? Reading between the lines of Sony's instructions, I think so, but I'm not yet positive. In the worst case, I'll need to redownload them from Sony's online store in the new ePub format. More generally, the trail of history is already littered with plenty of examples of obsolete services and associated hardware that left consumers who'd paid plenty of precious money hanging high and dry."EDN

## REFERENCES

- Nelson, Rick, "E-readers obsolete?" *Test & Measurement World*, Dec 2, 2009, www.tmworld.com/blog/Taking\_the\_Measure/26551-E\_readers\_obsolete\_.php.

- Fowler, Geoffrey A, "E-Readers: They're Hot Now, But the Story Isn't Over," *The Wall Street Journal*, Dec 7, 2009, www.wsj.com.

- Dipert, Brian, "Digital-media obsolescence: Sony's eBook acquiescence," *EDN*, Dec 16, 2009, www. edn.com/blog/400000040/post/1530051353.html.

Contact me at rnelson@reedbusiness.

### PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

## PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

## ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@reedbusiness.com

### **EDITOR-IN-CHIEF, EDN WORLDWIDE**

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

### **EXECUTIVE EDITOR**

Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161;

amy.norcross@reedbusiness.com Contact for contributed technical articles

### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

## MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

## **NEWS**

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

## POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

## DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

### SENIOR ASSOCIATE EDITOR

Frances T Granville

1-781-734-8439; fax: 1-303-265-3131;

f.granville@reedbusiness.com

### **EDITORIAL/WEB PRODUCTION**

Diane Malone, Manager

1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney,

Production/Editorial Coordinator

1-781-734-8442; fax: 1-303-265-3198 Melissa Annand,

Web Operations Specialist

1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi,

Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

### CONSULTING EDITOR

Jim Williams, Staff Scientist, Linear Technology

## CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

## EDN EUROPE

Graham Prophet, Editor, Reed Publishing +44 118 935 1650; gprophet@reedbusiness.com

## EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

## **EDN CHINA**

William Zhang,

Publisher and Editorial Director

wmzhang@rbichina.com.cn

Jeff Lu, Executive Editor

jefflu@rbichina.com.cn

## EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.geffreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

## MAXIMUM)

## RELIABILITY

In contact, stability and low-noise performance

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

**SLC Connector Assemblies**

Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

www.mill-max.com/EDN596

## 32-bit processor pushes deeper into 8-bit territory

XP's 50-MHz ARM (www.arm.com) Cortex-M0-based LPC1100 microcontroller family represents the latest 32-bit challenge to 8- and 16-bit processors. The parts are available now with prices starting at 65 to 95 cents (10,000). They have onchip flash covering 8, 16, 24, and 32 kbytes in a 33-pin package; 48-pin LPQFP

and PLCC44 packages are also available. The company claims that the EEMBC (Embedded Microprocessor Benchmark Consor-LPC1100 tium, www.eembc.org) Core-Mark Benchmark measures 40 to 50% better code density for

the LPC1100 than that of 8- and 16-bit microcontrollers. Efforts are in progress to further evaluate why the CoreMark code density is better on the 32-bit architecture.

The LPC1100 supports 32 vectored interrupts with four priority levels, and it includes one UART (universal-asynchronous-receiver/transmitter) interface; as many as two SPIs (serialperipheral interfaces); FM+ (fast-mode plus) I<sup>2</sup>C (inter-integrated-circuit) support; and two 16- and 32-bit timers with PWM (pulse-width modulation), match, and capture. The eightchannel, 10-bit ADC is accurate to ±1 LSB (least-significant bit) DNL (differential nonlinearity). The device supports power-on-reset, multilevel brownout detection, and a 10- to 50-MHz PLL (phase-locked loop). The 12-MHz in-

> ternal RC oscillator maintains 1% accuracy over the temperature and voltage range. The GPIO (generalpurpose-input/output) pins are 5Vtolerant, and some pins support as much as 20-mA drive. Software-de-

The LPC1100 microcontroller family represents the latest 32-bit challenge to 8- and 16-bit processors.

velopment tools are available for the LPC1100 from IAR Systems (www. iar.com), Keil (www.keil. com), Hitex (www.hitex. com), and Code Red

Technologies (www.code-red-tech.com). NXP will also offer a development-tool platform for less than \$30.-by Robert Cravotta

▶NXP, www.nxp.com.

- FEEDBACK LOOP "If my microprocessor can evaluate one configuration in one microsecond, it will take 13.3 hours to go through 48 billion if I did the math correctly. Are they using cloud computing?"

-Applications engineer Harry Holt, in EDN's Feedback Loop, at www.edn.com/article/ CA6705379. Add your comments.

## ICs tackle accuracy in multiphase-metering applications

Addressing the need for accuracy in multiphase metering, Analog Devices recently announced four energy-metering chips that focus on improving the accuracy and performance of commercial, industrial, and residential smart meters. The ADE7878, ADE7868, ADE7858, and ADE7854 chips target use in polyphase configurations, including three- and four-wire wye and delta services. The devices measure both reactive and active energy with 0.1% accuracy. The ADE7878 can measure fundamental-only energies that power-quality measurements use. The ICs feature 0.1% accuracy for both active- and reactive-energy measurements over a dynamic range

of 1000 to 1 and 0.2% accuracy over a dynamic range of 3000 to 1. Prices range from \$5.34 (1000) for the most basic version to \$7.47 for the ADE7878.

The Analog Devices announcement comes as the Smart Grid increases robustness and reliability and integrates renewable energy into the power grid. These goals bring sizable challenges, such as accurately measuring and com-

municating power-usage data. In the United States, 18 million homes will get smart meters within three years. For more on the challenges and applications of smart meters, go to www. edn.com/100107pa.

-by Margery Conner ▶Analog Devices, www. analog.com.

ADE78XX family of smart-meter chips measures both reactive and active energy with 0.1% accuracy.

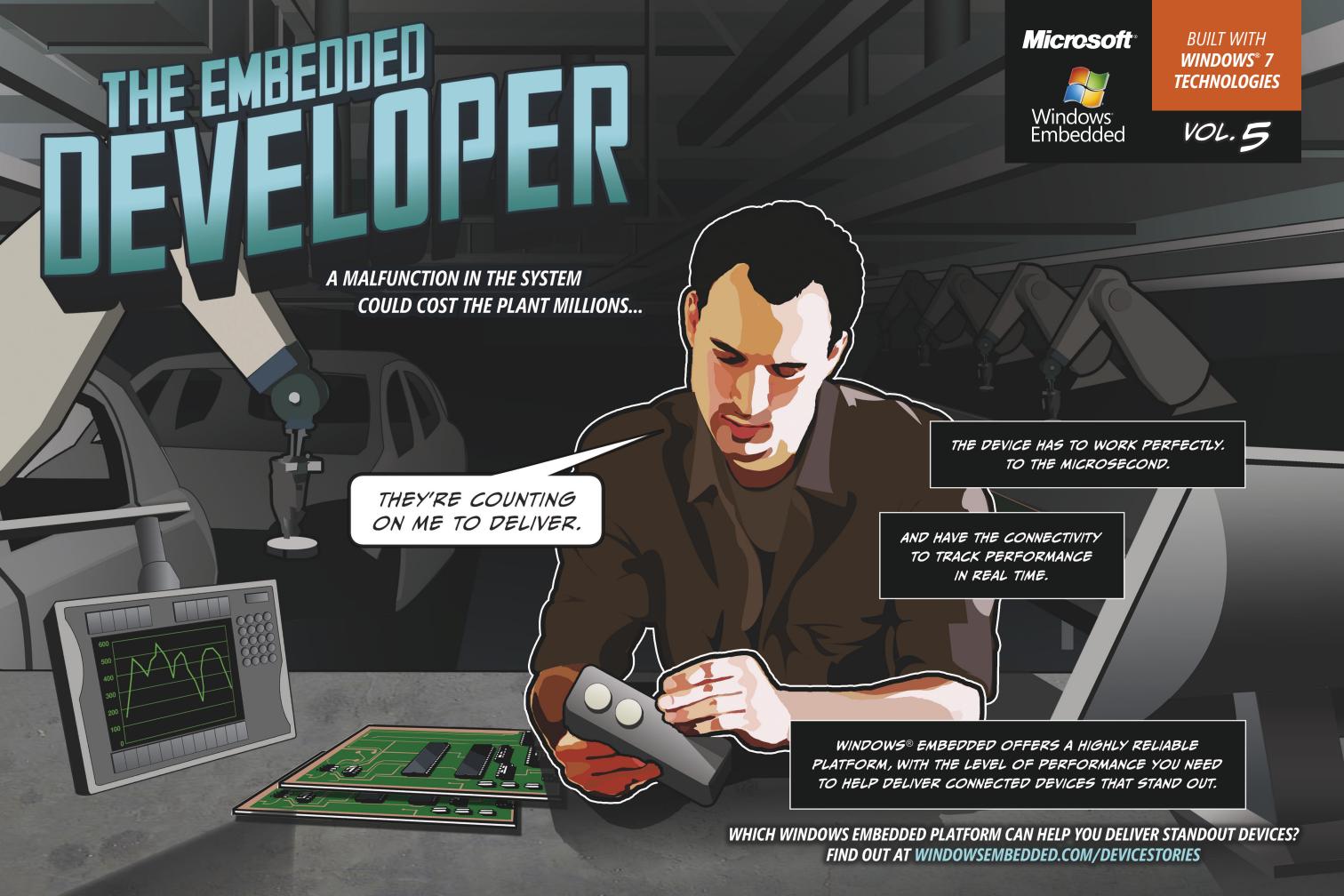

## Chip provides speedy MPEG transcoding, trans-scaling

enverge claims that its new ZN200 chip transcodes MPEG-2 and various MPEG-4 video flavors in high definition at speeds as much as four times greater than real time. The ZN200 also promises to downscale HD (high-definition) video to

MAC=MEDIA-ACCESS CONTROL

OTG=ON-THE-GO

**FXPRFSS**

MOCA=MULTIMEDIA OVER COAXIAL

PCIE=PERIPHERAL COMPONENT INTERCONNECT

portable-device resolutions at as much as 40 times real-time rates, according to the company. An accompanying sonic processor handles conversion between AAC (advanced audio coding), AC (audio-codec)-3, MP3, and other audio formats, and the ZN200 also internally

converts between various DRM (digital-rights-management) standards. The lower-priced ZN100, whose price Zenverge has not yet announced, has half the video-processing performance of its ZN200 sibling.

According to Tony Masterson, Zenverge's co-founder, technology officer, the chip enables users to control the format, resolution, size, and speed of transcoding. The chip transcodes US terrestrial-broadcast content in MPEG-2 format into the H.264 format that portable video players and cell phones support. The ZN200 transscales the content from high or main profile to the baselineprofile H.264 that cell phones require and scales the resolution of HD content from either 1920×1080 or 1280×720 pixels into cell-phone resolution of 320×240 pixels. It also converts 30-frame/sec content to the 15-frame/sec content that cell phones can handle, requiring sophisticated conversion between compressed I (intracoded), P (predicted), and B (bidirectionally predicted) pictures. Although some of these abilities may represent overkill for your application, consider that Zenverge's packet-processing architecture alternatively allows the chips to concurrently handle multiple streams with little to no efficiency loss. Such an approach might, for example, enable a set-top box to record one or a few channels while playing back another in a timeshifted manner.

chief operating officer, and chief

Recent demos of a ZN200 on a one-lane PCIe (Peripheral Component Interconnect Express) add-in card encompassing video encoded at various bit rates, resolutions, and formats came impressively close to the company's claims, and company officials were quick to point out that the chip was running code that was not performance-optimized and was full of speed-strapping debugging routines. The chip sells for \$50 (sample quantities).

-by Brian Dipert >Zenverge, www.zenverge. com.

The ZN200 chip transcodes MPEG-2 and various MPEG-4 video flavors in high definition at speeds as much as four times greater than real time.

STB=SET-TOP BOX

TS=TRANSPORT STRFAM

RECEIVER/TRANSMITTER

USB=UNIVERSAL SERIAL BUS

UART=UNIVERSAL ASYNCHRONOUS

**DILBERT By Scott Adams** I FIND IT RATHER THAT'S YOU YOU'VE DEMOTIVATING THAT BECAUSE WOULDN'T HAVE NEVER YOU NEVER PRAISE ME THAT MAKE I'M DE-TO GO DONE FOR A JOB WELL DONE. MOTI-FIRST. ME THE A JOB VATED. LEADER? WELL.

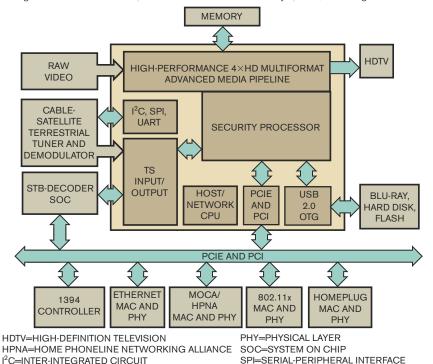

## 16-bit, dual-channel ADCs span 20M to 80M samples/sec

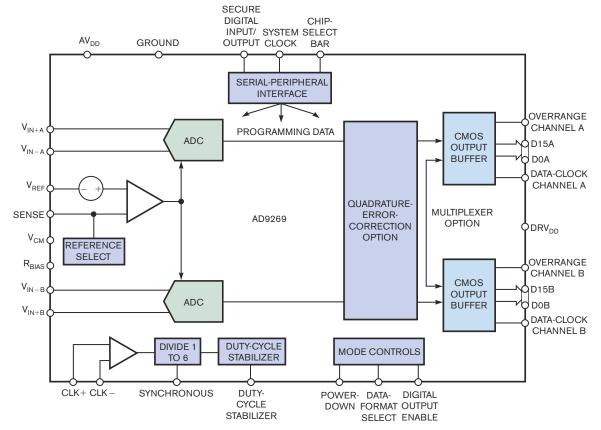

nalog Devices' new AD9269 family of 20M-, 40M-, 65M-, and 80M-sample/sec pipeline ADCs takes 16-bit samples. The units consume 42 to 93 mW of power, depending on speed, and they integrate both a reference and a sample-and-hold circuit. The differential-input stage features a 700-MHz bandwidth, and output data is on separate parallel interfaces for each channel.

Targeting use in wireless base stations, the ADCs feature a quadrature-decoding error-correction block to improve the performance of an I/Q (in-phase/quadrature) complex-signal receiver system.

They operate from a 1.8V analog supply and a 1.8 to 3.3V power supply for the output

section. SNR (signal-to-noise ratio) is 77 dBFS (decibels relative to full-scale) at a 10-

The AD9269's SNR performance depends on the quality of the signal you use to clock it. Low-jitter clock inputs are essential for best performance.

MHz input and 73 dBFS at a 170-MHz input frequency. The SFDR (spurious-free dynamic range) is 90 dBc (decibels referenced to the carrier) at 10 MHz and 78 dBc at 170-MHz input frequencies. The ENOB (effective number of bits) is 12.4 for inputs of 9.7 to 30.5 MHz, 12.2 for inputs of 70 MHz, and 11.6 for input frequencies of 170 MHz.

The AD9269 is available in a 9×9-mm, 64-pin LF-CSP with suggested retail prices of \$49, \$59.50, \$73.66, and \$84.09 (1000) for the 20M-, 40M-, 65M-, and 80M-sample/sec versions, respectively. They operate over a -40 to +85°C temperature range. Production quantities are now available.—by Paul Rako

► Analog Devices, www. analog.com.

The AD9269 contains a quadrature-decoding error-correction block for wireless-base-station-receiver chains.

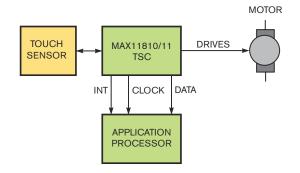

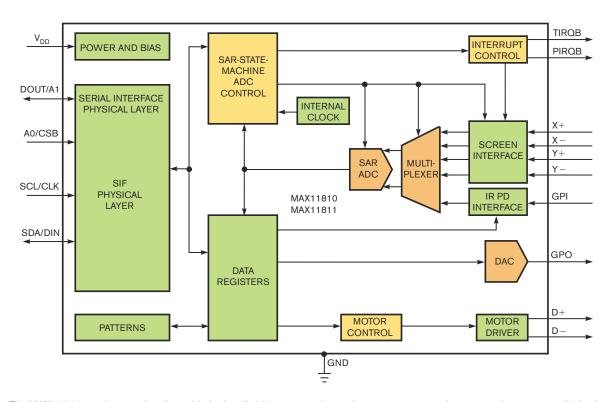

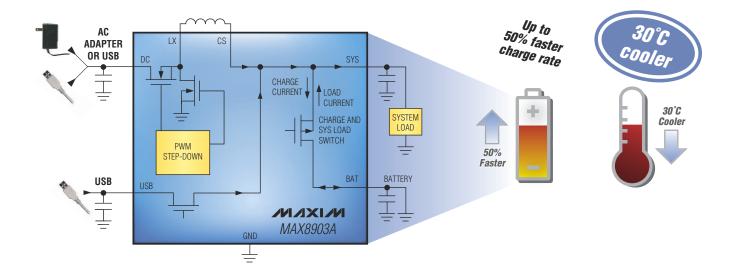

## Touchscreen controller provides tactile feedback

axim Integrated Products recently announced the MAX-11810 touchscreen-interface chip. The device generates the output voltage to excite a fourwire resistive touchscreen and includes ADCs to read back a touch position. It also provides haptic feedback by rotating a vibrator motor or pulsing a piezoelectric transducer on the LCD screen. It excites and reads back an IR (infrared) photodiode to sense when the screen is pressed against your face. This feature allows it to ignore the inputs and suppress the haptic outputs. A sister part, the MAX11811, has identical functions but employs a 400-kHz I<sup>2</sup>C (inter-integrated-circuit) interface instead of a 25-MHz SPI (serial-pe-

The MAX11810 contains the circuitry to drive a touchscreen, a haptic tactile-feedback device, and a photodiode. The part has an SPI, and the MAX11811 uses an I2C interface.

ripheral interface). Both parts operate from a 1.7 to 3.6V power supply and feature 12bit ADCs. At a 34.4k-sample/ sec rate, the device consumes 246 mW at 1.8V or 698 mW at 3.6V.

Applications include cell phones, MP3 players, portable media players, digital photo frames, multifunction printers, point-of-sale terminals, bar-code scanners, card readers, and other industrial equipment. Automotive-qualifiedpart versions exist for use in car GPSs (global-positioning systems), entertainment head units, and rear-seat entertainment systems.

The product has a state machine for onboard processing of touch events to validate them before sending the data to the system microprocessor. The onboard processing can also supply an improved capture rate of as many as 161 coordinates/sec.

The MAX11810 operates over a -40 to  $+85^{\circ}C$  temperature range and comes in 2.1×2.1-mm, 20-pin TQFN packages and 16-pin WLPs. It sells for \$1.81 (1000) and is available now, along with evaluation kits that include a touchscreen and a dc motor.

-by Paul Rako ►Maxim Integrated Products, www. maxim-ic.com.

The MAX11810 touchscreen-interface chip for handheld consumer electronics can process touch events and output a tactile feedback without waking up the system application processor.

## Analog FastSpice RF delivers noise analysis for RF circuits

erkeley Design Automation Inc has announced AFS RF (Analog FastSpice radio frequency), which Chief Operating Officer Paul Estrada calls the industry's first true Spice-accurate noise-analysis tool for RF circuits. AFS RF accurately analyzes nanometer-scale device-noise impact for all types of prelayout and postlayout circuits, ensuring early insight into its impact on performance, power, and area.

Before the emergence of AFS RF, designers had to use limited-spectrum RF tools that can only approximate device-noise impact on RF circuits, Estrada explains. Such approximations are increasingly inaccurate with decreasing process geometries, often becoming grossly inaccurate in nanometer-scale circuits. Circuits with sharp transitions,

Without accurate analysis, designers must include expensive design margin.

such as switched-capacitor filters, charge pumps, and dividers; high-frequency circuits, such as RF front-end blocks; and oscillators are especially sensitive to these inaccuracies. Without accurate analysis, designers must include expensive design margin or risk missing specifications in silicon.

Using the industry's first fullspectrum device-noise-analysis engine, AFS RF provides true Spice accuracy for every run. For complex circuits, it is five to 10 times faster than traditional RF tools that can only approximate device-noise effects. AFS RF features the DNA (device-noise-analysis) Advisor to characterize DNA requirements, high-capacity periodic-steady-state analysis for greater than 100,000element postlayout circuits, full-spectrum periodic-noise analysis with true Spice accuracy, full-spectrum total oscillator-device-noise analysis with phase and amplitude noise, and harmonic balance for fast single-tone analysis of moderately nonlinear circuits.

"We have been using the AFS platform for the last two years for full-circuit transceiver verification and more recently transient-noise analysis of our analog/RF blocks," says Alan Wong, head of IC design at Toumaz Technology (www. toumaz.com). "AFS RF delivers

full-spectrum periodic noise analysis and does not trade off accuracy for performance. AFS RF allows us to analyze our prelayout and postlayout RF blocks, delivering true Spice accuracy and a five- to 10-times speedup over traditional RF-analysis tools."

"Full-spectrum periodic noise analysis is critical for accurate characterization of device noise in nanometer analog/RF designs," says Boris Murmann, PhD, assistant professor in the department of electrical engineering at Stanford University (www.stanford.edu). "Without accurate device-noise analysis, designers need to add significant margin to ensure performance. This [addition] can be very expensive. For example, adding just 0.5 bit of marginthat is, 3-dB SNR (signal-tonoise ratio)-in a noise-limited circuit will double the required power."-by Rick Nelson ▶Berkeley Design Automation Inc, www. berkeley-da.com.

## FUNCTION-LEVEL VISIBILITY IMPROVES APPLICATION OPTIMIZER

As processor architectures enable developers to build ever-more-complex applications, the software-development tools that speed and improve the process increase in value. For example, the Ceva-Toolbox software-development environment now includes an application-optimizer tool chain that provides software optimization for code targeting Ceva's DSP cores. The tool enables developers to generate target code completely in C that performs within 20% of the performance of hand-optimized assembly. The tool-chain optimizers assist development throughout design and building and include a project optimizer, an application profiler, scoring-based compilation, a postlinker optimizer, and automated test generation. The tool chain is now available.

The project-build optimizer enables you to automatically build multiple configurations based on compiler settings at individual function levels. The tool chain supports the automated simulation, profiling, and down-selection of these multiple configuration scenarios to help find the best match of the application requirements and the system resources. The application profiler includes a cycle-

accurate C-level application and memory-subsystem profiler that enables the tool chain to detect applicationand system-level bottlenecks by taking into account the full memory subsystem. The scoring-based compilation component supports multiple iterative compilation levels to allow trade-offs between cycle count and code size on a C-level, function-by-function basis. The postlinker optimizer works with a global view of the application within the system and resolves resource scenarios that you cannot completely address during compilation and that further enable smaller application code. The automated test generation provides full test suites and supports standard Perl scripts. The tool chain also supports the inclusion and integration of C-callable assembly-optimized functions as a native part of the compiler's standard libraries. The debugger supports connectivity features with external tools to simplify migration of algorithms, such as those from The MathWorks' (www.mathworks.com) Matlab, so that parts of the code can run within Matlab or on the debugger.-by Robert Cravotta

Ceva, www.ceva-dsp.com.

SEARCH UPDATE

EDITED BY FRAN GRANVILLE

## Micro-ants act as tiny conveyor belts inside chips

esearchers at the Massachusetts Institute of Technology's department of materials science, in collaboration with researchers in Germany and from Boston University (www.bu.edu), have devised a microscopic system that could provide a novel method for moving tiny objects inside a microchip and could provide new insights into how cells and other objects move around within the body. Organs such as the trachea and the intestines have cilia, tiny, hairlike filaments that are constantly in motion, beating in unison to create currents that sweep along cells, nutrients, or other tiny particles. The new research uses a self-assembling system to mimic that kind of motion, providing a simple way to move particles around in a precisely controlled way.

Alfredo Alexander-Katz, a professor of materials science and engineering; his doctoral student Charles Sing; and other researchers devised a system that uses tiny so-called superparamagnetic beads made of polymers with specks of magnetic material in them. Due to the heavy magnetic material content, these beads sink to

the bottom of the sample. By applying a rotating magnetic field, which caused the beads to spontaneously form short, spinning chains, the researchers created currents that could then carry along surrounding particles as much as 100 times larger than the beads themselves. Alexander-Katz Chains of superparamagnetic colloidal particles rotate to produce flows on length scales much larger than the chain, allowing them to behave like micro-ants that can move large particles (courtesy Charles Sing and Alfredo Alexander-Katz, MIT).

refers to the microscopic assembly of beads-each just a few microns in size-as microants because of their ability to move while "carrying" objects so much larger than themselves (Reference 1).

The new method could provide a simpler, less-expensive alternative to currently available microfluidic devices, a field that is still in its early stages of development. Such devices now require precisely made channels, valves, and pumps using microchip-manufacturing methods to control the movement of fluids through them. The new system could offer such precise control over the movement of liquids

A biochip-based diagnostic

ume than other techniques.

test requires less sample vol-

and the particles suspended in them that it may be possible to dispense with the channels and other plumbing altogether, controlling the movements entirely through variations in the applied magnetic field. In other words, software rather than hardware could control the chip's properties, allowing you to instantly reconfigure it through changes in the controlling software.-FG

▶ Massachusetts Institute of Technology, www.mit.edu.

## REFERENCE

Sing, Charles, Lothar Schmid, Matthias F Schneider, and Alfredo Alexander-Katz. "Controlled surface-induced flows from the motion of self-assembled colloidal walkers." Proceedings of the National Academy of Sciences, Dec 14, 2009, www.pnas.org/ content/early/2009/12/17/ 0906489107.abstract.

## Biochip-based test aims at speedy disease diagnosis

IBM scientists have built a biochip-based, one-step point-of-care diagnostic test that reguires less sample volume and is significantly faster than currently available techniques. An article in the December 2009 issue of Lab on

a Chip describes the research. The portable, easy-to-use system can test for many diseases, including cardiovascular disease. IBM Research-Zurich scientists Luc Gervais and Emmanuel Delamarche, in collaboration with the University Hospital of Basel in Switzerland, developed the test, which uses

capillary forces to analyze samples of serum, or blood, for the presence of disease markers. Capillary-action force is the tendency of a liquid to rise in narrow tubes or to be drawn into small openings.

IBM encoded the forces of capillary action on a microfluidic chip made of a silicon compound, measuring 135 cm and containing sets of micronwide channels in which the test

sample flows through in approximately 15 sec-several times faster than traditional tests. Further, you can adjust the filling speed to several minutes when the chip requires additional time to read a more complex disease marker.

> The microfluidic chip works with a 1-microliter sample-50 times smaller than a teardrop—that the researchers move onto the chip using a pipette. The capillary forces then begin to push the sample through an intricate series of mesh structures. The sample passes into a region

into which researchers have deposited microscopic amounts of the detection antibody. The test uses only 70 picoliters-1 million times smaller than a teardrop-of these antibodies, making for their fast and efficient dissolution in the passing sample. For more, go to www. edn.com/article/CA6708422.

-by Suzanne Deffree **▶IBM Research-Zurich**, www.zurich.ibm.com.

## BY HOWARD JOHNSON, PhD

## It's a Gaussian world

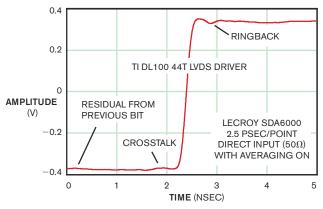

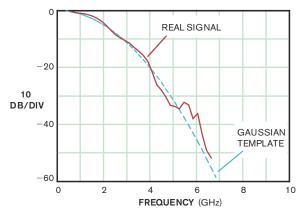

previous article suggests that most digital output waveforms follow a nearly Gaussian profile (Reference 1). Let's test that theory.

Figure 1 depicts the rising edge from a Texas Instruments (www.ti.com) DL100 44T LVDS (low-voltage-differential-signaling) driver. This driver exists on a custom test board with SMA output connectors. A coaxial cable feeds the test outputs directly to the  $50\Omega$  terminated inputs of a LeCroy (www.lecroy.com) SDA6000 oscilloscope. A small bit of residual ringing from the previous bit appears in the left side of the figure. Then, just before the signal begins its major

ascent, you may see a tiny precursor, probably the result of crosstalk from the test equipment and predrivers inside the DL100 44T. The amplitude of these features amounts to only about 1% of the main signal's step size.

Directly after the main edge, the signal overshoots a tiny amount and then rings back approximately 2%. This artifact is more likely due to the layout of the test board than anything related to the DL100 44T. With artifact amplitudes this low, spectral analysis of the waveform should clearly reveal whether the true spectral content

of a DL100 44T driver follows the Gaussian theory.

Figure 1 plots the step response of the driver. Spectral calculations require the impulse response. The frequency response associated with that impulse response gives you a filter you can then apply to any square-edged digital signal, making the output look just like the step shapes in Figure 1.

To make the necessary spectral calculations, first convert the step waveform to an impulse response by computing, at each point, the slope of the signal:

$$x_n' = (x_{n+1} - x_n)/T,$$

where *T* equals the sampling interval. Next, truncate the signal to a finite-length region. Make the region wide enough to capture the main features of the signal in question but narrow enough to eliminate unrelated events before and after the main edge. Try using the whole region shown in **Figure 1**, from 0 to 5 nsec. Within this region, 2000 points are sampled at 2.5 psec each.

Simple truncation of a sampled-data sequence can induce Gibbs phenomena. To mitigate these unusual effects, multiply the truncated sequence by a Hamming window of length N=2000:

$$h_n = 0.54 - 0.46 \cos(2\pi n/N).$$

A Hamming window smoothly feathers the sequence to zero at both ends, reducing the impact of discontinuities at the endpoints. It accomplishes this task at the expense of a modest loss in frequency-domain resolution.

Finally, use an FFT to compute the frequency response of the windowed impulse response and normalize the result so that it starts at 0 dB. Figure 2 compares the result against a Gaussian template. It's a match.EDN

## REFERENCE

■ Johnson, Howard, "Real signals," *EDN*, Oct 8, 2009, pg 13, www.edn. com/article/CA6699737.

Figure 1 Small artifacts precede and follow each edge.

Figure 2 The real signal follows a Gaussian template.

## MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

## INSIDE NANOTECHNOLOGY

## BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

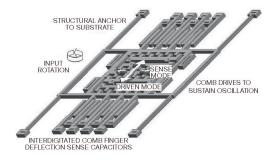

## MEMS, sensors, and nanotechnology

he relentless pursuit of more transistors in a smaller area has driven the semiconductor industry since its start. This drive has now produced sophisticated SOCs (systems on chips) that include billions of transistors per design for memories and microprocessors. The costs of these large designs on small geometry processes make for a \$50 million to multibillion-dollar project. Because of these costs, the advanced design work is being performed by significantly fewer development teams and companies and is outside the scope of most start-ups.

In contrast, MEMS (microelectromechanical systems), solid-state sensors, and new applications of nanotechnology are rapidly gaining in importance and diversity. These areas of creative design activity require a stronger interaction between design and processing technology. The result of this interaction is the modification and advancement of the process technology as well as the creation of new designs and design methods.

Recent advances in the data-processing capability in electronics products have given rise to new and smaller MEMS products and to new functions. Some of these new functions

and applications that people encounter regularly are air-bag accelerometers, tire-pressure monitors, 2- and 3-D gyroscopes for GPS (global-positioning-system) devices, gyroscopes for video-game motion controllers, and rotation controllers for cell-phone displays. You can see the complexity of some of these new designs from a typical MEMS gyroscope (Figure 1).

Sensor technology has long focused on image sensing and pressure sensing as baseline markets. New technologies have additionally brought about huge advances in the design of microfluidic and nanofluidic sensors, chemical and gas sensors, vibration and enhealth-care-product designs. These new solid-state devices depend on the low cost of semiconductor manufacturing to meet the volume and price points necessary for mass commercialization and the reduction in power and increase in effective signal integrity to be compatible with digital signal processing with either wired or wireless connectivity.

Nanotechnology is a growing area of multiple disciplines and definitions. The general consensus is that the word "nanotechnology" refers to devices and materials that are complete objects smaller than 100 nm. This definition includes semiconductor processes and lithography at the 65- to 22-nm nodes. graphine- and carbon-nanotube structures, and most structures and materials that designers create using catalyzed self-assembly. Nanotechnology design includes active devices, passive devices, and mechanical structures. These design objects find application in solarenergy collection, nanomedicine, photonics, and electronics. Some of the more exotic electronics devices possible are the recently discovered memristor, finfets, and other 3-D transistors.

The new technologies address societal and industrial issues, such as monitoring of vibration and wear on the structural aspects of bridges and buildings, creation of portable and intelligent-clinic-use medical-diagnostics equipment, automated access control and asset management, a more human interface to computing platforms, and increased operation safety in transportation systems. The reduced size, power requirements, and cost of manufacturing along with available distributedcomputing resources will make sensors and sensor signal processing ubiquitous in most products in the future. The creation of circuits and systems with these design elements is an iterative task with both design exploration and technology development taking turns as the driver in the loop. **EDN**

ergy-harvesting sensors, and temperature sensors. Recent advances, such as the November 2009 announcement of technology licensing for audio sensors for the design and manufacture of MEMS microphones between ST-Microelectronics (www.st. com) and Omron (www. omron.com), are bringing about new cell-phone, laptop, mobile-Internet, and

Figure 1 A typical MEMS gyroscope is complex (courtesy Steve Beeby, MEMS Mechanical Sensors).

Contact me at pallabc@siliconmap.net.

## The Avago Advantage

## Renewable Energy Applications: Reliability and Safety with Fiber Optic and Optocoupler Isolation Technology

## Introduction

Climate change, rising carbon dioxide levels, environmental pollution and volatile fossil fuel prices have driven electric power generation producers, governments, and individual consumers to adopt alternative energy generation methods such as solar and wind. Governmental renewable energy support has been incorporate into strategic energy plans worldwide. During 2009 at least 73 countries had energy policy targets and more than 64 countries had policies to promote renewable power generation. Renewable energy is no longer an area dominated by research, but rather a large commercial market with high adoption and installation growth rates.

Renewable energy growth in 2008 was substantial and 2009 activity points toward continued progress. The United States ended 2008 with 25 GW of wind power, eclipsing Germany's 24 GW capacity. China's total wind power doubled for the fifth year in a row, ending the year above 12 GW, exceeding China's 2010 development target of 10 GW two years ahead of plan. More than 80 countries around the world now have commercial wind power installations.

With most 2008 offshore wind generation capacity in Europe, capacity reached nearly 1.5 GW. The United Kingdom became the offshore wind power leader in 2008 but other countries, such as the United States, have plans for new offshore facilities.

Grid-connected solar photovoltaic plants are the fastest growing power generation technology, with a 70-percent increase in existing capacity to 13 GW in 2008. This was a six fold increase in global capacity since 2004. Including off-grid applications, total 2008 photovoltaic generation increased to over 16 GW. In 2008, utility-scale solar PV power plants—plants over 200 kW—were estimated to have grown by 80%, to 1,800, since 2007. The added plants totaled over 3 GW, a tripling of existing 2007 capacity.

Utility photovoltaic plant additions were a major 2008 focus in Spain but facilities also went into the Czech Republic, France, Germany, Italy, Korea, and Portugal. New solar photovoltaic plants are planned and under development throughout Europe as well as China, India, Japan, and the United States.

Given the high growth rates and importance of renewable energy, Avago focused its fiber optic and isolation product portfolios and product development efforts toward renewable energy applications. Digital optocouplers, gate drivers, isolation amplifiers and solid state relays provide safety isolation and insulation along with their basic function. Fiber optic components, besides providing isolation, provide EMI resistant, long distance communication channels in wind turbine farms and panel-to-panel communications in solar photovoltaic systems. These control and communication channels are critical for safety and optimal power efficiency in distributed solar systems and especially for offshore wind farm installations.

## **Avago Renewable Energy Solutions**

Avago Technologies offers fiber optic transmitters, receivers and transceivers, as well as IGBT and Power MOSFET gate drivers and optocoupler isolation products for wind turbine, wind farm and solar electric power generation.

Avago fiber optic components, isolated gate drivers, isolation amplifiers and digital optocouplers are deployed in wind turbines, wind farms and solar photovoltaic energy farms today.

Applications include:

- Power rectifiers and inverter power assemblies

- · Control and communication boards

- Turbine control unit condition monitoring systems

- Wind farm networks

- Sun tracking control

- Communications boards

- Solar farm substation automation and protection relays

- Single- and three-phase inverters

- Battery chargers

- Motor control

- DC-to-DC converters,

- System control and monitoring

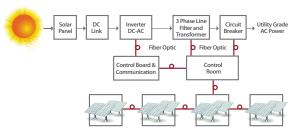

## **Solar Energy: Fiber Optic Solutions**

Avago fiber optic transceivers provide control and communication links within a solar energy system and within the solar farm. Resistant to EMI and able to withstand rugged environments, Avago transceivers support POF, HCS and Multimode fiber. Plastic cable supports transmission up to 50 m. For longer distances 200  $\mu m$  HCS and 62.5/125  $\mu m$  fiber will support up to 2,700 m links. Maximum transmission distances, depending on data rates, are up to 80 km.

Data rates from 1/5/10/20/160 MBd are available with many different connector styles: LC, SC, SFP and MT-RJ.

Figure 1. Fiber data links in solar energy farm

## Wind Turbine Networking, Control and Communications: Fiber Optic Solutions

In wind turbine applications access for maintenance and repair is more limited than in land-based solar farms. This is especially true for off shore wind generation installations. In addition, large mechanical loads and changing local weather conditions must be monitored in near real time for optimal power generation, safety and control. Long term reliability and quality are very important component selection factors.

Inside the turbine nacelle, short range fiber optic connections connect power generation subsystems and the turbine pitch controller to the main system controller. Avago offers a broad portfolio of fiber-optics transmitter and receiver like the HFBR-0500Z family which are used in Wind-Turbines since many

## The Avago Advantage Technical Notes

years. For Wind-Turbines >2 MW the main choice inside the turbine is fiber optics because of EMI, lightning and galvanic isolation. Longer range fiber links connect to tower base and the wind farm

In turbine monitoring and solar systems, Fast Ethernet transceivers with DMI and SC-RJ connectors, such as the Avago AFBR-5978Z, are popular as they operate at 650  $\mu m$  over POF and HCS cable and feature a  $-25^{\circ}\text{C}$  to  $85^{\circ}\text{C}$  temperature range. A demonstration kit for the AFBR-5978Z (AFBR-0978Z) is available from any Avago sales offices or representative.

Our new multimode, small form factor (SFP) HFBR-57E5APZ Fast Ethernet transceiver with DMI requires only 611 mW and operates from 3.3 V.

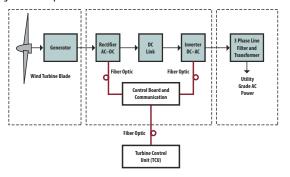

Figure 2. Fiber optic communication links in wind turbines

## Solar and Wind Power: Application Specific Optocouplers, Gate Drivers and Isolation Amplifiers

As the leading optocoupler supplier, Avago develops application specific isolated power MOSFET gate and IGBT drivers for power applications. Featuring high peak output current, high CMR, wide temperature range, low supply current, surface mount packages and integrated protection circuits they are ideal for motor control, inverter and battery charging circuits.

The ACNW3190 isolated gate driver has a 5 A peak drive current and under voltage lockout (UVLO) protection. Other devices have 0.4 A to 2.5 A peak drive current. For maximum reliability and design flexibility, Avago devices have protection features such as integrated VCE detection, UVLO, "soft" IGBT turn-off, isolated opencollector fault feedback and active Miller clamping for maximum design flexibility and circuit protection. A Miller clamp controls the Miller capacitance current during high dV/dt transitions and can eliminate the need for a negative supply voltage.

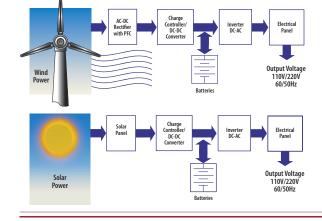

Figure 3. Isolation and insulation solutions in wind-solar power generation systems include inverters, charge controllers and communications.

Data subject to change. Copyright © 2009 Avago Technologies

With the Avago analog isolation amplifiers, current and voltage monitoring in motor control, inverter and battery applications is simple, safe and accurate. Phase currents and DC link voltages are easily measured while maintaining isolation. The amplifiers have working voltages of up to 1140 V for safety. Gain accuracy ranges from +1% to +5%.

The ACPL-796J 1-bit, second-order sigma-delta modulator converts an analog input signal into a high-speed data stream with galvanic isolation based on Avago's optical coupling technology. The ACPL-796J operates from a 5 V power supply with dynamic range of 80 dB with an appropriate digital filter. The differential inputs of  $\pm 200$  mV, full scale  $\pm 320$  mV, are ideal for direct connection to shunt resistors or other low-level signal sources in motor phase current measurement applications.

## Solar and Wind Power: Digital Optocouplers

Wind control systems must accommodate varying wind conditions and avoid run-to-failure by monitoring subsystems accurately. High voltage isolation, current isolation and immunity to EMI are critical for reliable and robust control systems. Solar and wind farms face harsh environmental conditions and operate over large physical areas susceptible to lightning and extreme temperatures. Avago digital optocouplers have the insulation and isolation specifications to make command and control systems safe and reliable. All our digital optocouplers are qualified to all international safety organization insulation and isolation specifications. Many devices have working voltages that exceed 1768 Vrms and isolation voltage up to 7500 Vrms are offered.

Operating at 10 MBd, multi-channel and bi-directional optocouplers (ACSL-6210/6310/64x0 in Dual/Triple/Quad channel) maximize design options and conserve PCB area. For extreme environments, the ACPL-M61U features –40°C to 125°C operation. The ACPL-M61L/061L/064L/W61L/K64L are ultra low power optocouplers suitable for energy efficient systems. Higher speed devices such as the ACPL-772L/072L operate at 25 MBd and from –40°C to 105°C.

Our photo MOSFETS, or solid state relays (SSRs), operate with voltages from 60 V to 600 V and with currents up to 2 A for energy storage management systems.

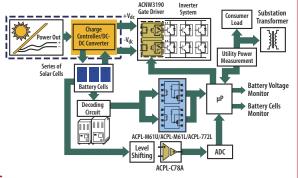

Figure 4. Isolated gate drive, digital optocoupler, level shifter and isolation amplifier applications.

## Summary

Innovative fiber optic and optical isolation solutions have been available from Avago for over three decades. As a major contributor to the work of international standards organizations, device reliability, quality and safety are always part of any Avago design. We offer the industry's best isolation technology, specifically designed and manufactured to meet the stringent requirements of applications in power generation systems.

Around the world our customers value what we do. We provide the components and technology to make their visions for the renewable energy market expand and prosper.

Contact us for your design needs at: www.avagoresponsecenter.com/401

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries.

AVAGO

Kevin C Craig, PhD,

chair in engineering

is the Robert C Greenheck

design and a professor of

mechanical engineering,

College of Engineering,

For more mechatronic

Marguette University.

## What's your point of view?

Time, frequency, and modal domains offer complementary views, insight.

ach of us is a critical-thinking problem solver. We have to be, as society's problems are mounting, getting harder, broader, deeper, and multidisciplinary. As basic engineering skills—analysis, hardware, and software—have become commodities worldwide, America's competitive advantage comes from being immediate, innovative, integrative, and conceptual. Our innovation must be local; you can't import it, you create it! It is a way of thinking, communicating, and doing. It differentiates us from other engineers around the world.

As multidisciplinary teams are formed to solve these problems, usually with a core group comprising mechanical, electronic, computer, and controls engineers together with problem-specific experts in, for example, combustion, chemistry, structures, materials, anatomy, and physiology, insight and communication are of utmost importance. We have all witnessed how engineers from different backgrounds describe the same concepts using different language and different points of view, which often can lead to confusion and, ultimately, design errors. Being able to describe concepts with clarity and insight in a variety of ways is essential for the mechatronics engineer as the multidisciplinary team leader.

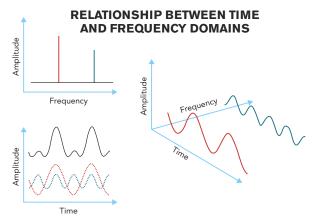

The two domains, time and frequency, represent different perspectives. They are interchangeable, complementary points of view—that is, no information is lost in changing from one domain to another—and together lead to better understanding and insight.

Time and frequency domains together give insight and enhance communication.

Most signals and processes involve both fast and slow components happening at the same time. In the time, or temporal, domain, we measure how long something takes, whereas in the frequency, or spectral, domain, we measure how fast or slow it is. No one domain is always the best answer, so the ability to easily change domains is quite valuable and aids in communicating with other team members.

A third domain, the modal domain, is particularly valuable in analyzing the behavior of mechanical structures. It breaks down complicated structural vibration problems into simple vibration modes. Unique

news, visit mechatronics zone.com. insight into the use of the modal domain in mechatronic system design has been provided in the work of Dr Adrian Rankers, manager of mechatronics technologies at Philips Applied Technologies.

The time domain is a record of the response of a dynamic system as indicated by some measured parameter, as a function of time. More than 100 years ago, Jean Baptiste Fourier showed that any real-world signal can be broken down into a sum of sine waves, and this combination of sine waves is unique. By picking the amplitudes, frequencies, and phases of these sine waves, one can generate a waveform identical to the desired signal. To show how the time and frequency domains are the same, the figure shows three axes: time, amplitude, and frequency. The time and amplitude axes are familiar from the time domain. The third axis, frequency, allows us to visually separate the sine waves that add to give us the complex waveform. Note that phase information is not represented here.

If we can predict the response of a system to a sine wave input—that is, the frequency response—then we can predict the response of the system to any real-world signal once we know the frequency spectrum of that signal. The system's frequency-response curves are really a complete description of the system's dynamic behavior.

Engineers who can bridge gaps among disciplines and articulate complementary points of view clearly and insightfully will certainly have a competitive advantage. EDN

## More measurements. More data. Less cost.

With up to 560 channels of data logging at a maximum scan rate of 1000 channels/sec, an internal 6  $\frac{1}{2}$  digit DMM with 22-bit resolution, and 0.03% accuracy, it's no mystery why Agilent's data acquisition systems are among the top selling in the world. The 34970A and 34980A are both at home with either data acquisition or functional test,

with a broad selection of plug-in modules. Now with Agilent Data Logger Pro software, you'll be able to collect data, check limits, perform extensive branching, and view and store the data without authoring the programming yourself. It's an ideal expansion at a significant savings.

www.agilent.com/find/daqswitch

u.s. 1-800-829-4444 canada: 1-877-894-4414

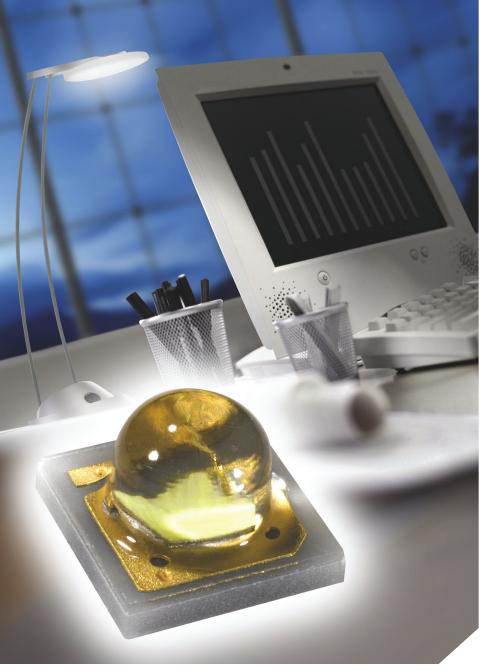

## INNOVATIVE PACKAGING

improves LEDs' light output, lifetime, and reliability

HB-LED PACKAGING DESIGN CONTINUES TO ADVANCE, CONTRIBUTING ALMOST AS MUCH TO PERFORMANCE AS THE LED CHIP ITSELF.

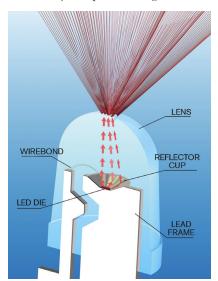

Figure 1 Manufacturers typically use SMT packages for 1 to 3W and higher-power HB LEDs because the close contact with the underlying PCB dissipates heat faster (left). Manufacturers typically use through-hole packages for 0.5W LEDs (above). An SMT HB LED includes the LED chip, the substrate, an encapsulant, and a primary lens.

B-LED (high-brightnesslight-emitting-diode) efficacy may grab the headlines, but packaging is where the action is in this market. Getting the light out of the die, through the encapsulant and lens, and onto the application's surface at a consistent, reliable color for a long lifetime is a challenge, and LED manufacturers accomplish this task through the use of innovative packaging for the devices. HB-LED users may be unaware that Big 4 manufacturers Cree, Nichia, Osram, and Philips Lumileds control almost all HB-LED chips. Although China is

all HB-LED chips. Although China is home to hundreds of LED-chip manufacturers, those vendors produce devices with only 10 to 70 mA of current, which eventually find use as indicators rather than illumination devices. The remaining HB-LED vendors are for the most part packagers of the tiny HB-LED chips that they purchase from the Big 4 manufacturers.

R&D efforts to coax more lumens from an LED die are enabling the use of LEDs in new markets and applications. Just as important, though, are manufacturers' packaging methods. These methods enhance efficiency to meet the needs of unique applications, such as solid-state-lighting, automotive, signage, and medical applications. To select the best HB LED for your application, you

need to understand its packaging as well as some of the methods its manufacturer used to squeeze out and precisely place as many photons as possible. Packaging affects light extraction, heat extraction, and lumen maintenance—important characteristics of LEDs. Light extraction determines how much emitted light will reach the intended application; thermal extraction affects how much heat the LED chip will experience and, hence, its lifetime and performance; and lumen maintenance indicates the lifetime of the LED. The HB-LED package determines—or at least strongly influences all three of these characteristics, which in turn affect the LED's performance, lifetime, and reliability.

HB LEDs currently have no standardized package footprint. Unlike for other electronic components, such as ICs, MOSFETs, and most passive components, every HB-LED manufacturer uses a unique package. This practice can be annoying to LED designers who want to line up second sources for their products, but LED packages comprise intricate combinations of the LED chip, encapsulant, primary optics, and substrate. The package for a 20- to 70-mA indicator-type LED dissipates heat through its leads. The epoxy encapsulant serves as a lens and provides a rigid protective structure for the die and leads. Compared with low-power LEDs, HB LEDs must rely on greater heat-dissipation capability for their packaging, and they typically come in SMT (surface-mount technology) or through-hole packages (Figure 1). SMT tends to find use in HB LEDs of 1W or higher power because it mounts directly onto a heat sink, whereas through-hole packages generally suit midrange HB LEDs of 0.5 to 1W.

An LED chip generates light in an epitaxial structure. Ideally, all of the hole/electron combinations would result in photons. Material characteristics and imperfections, however, cause some of the combinations to produce heat rather than light. The next challenge is getting the photons out of the die because of the difference in index of refraction between the layers of the chip, the encapsulant, and the lens. Air has an index of refraction of approximately one, whereas some die materials have an index of approximately 1.4. A difference in indexes for two materials causes light to reflect back at the boundary when the light exceeds a

## AT A GLANCE

- Relatively few manufacturers provide most HB-LED (high-brightness-light-emitting-diode) chips to the industry.

- Although Big 4 vendors manufacture and package their own LED chips, they also sell to other LED vendors that specialize in packaging HB LEDs for specialized applications.

- Light extraction, thermal extraction, and lumen maintenance affect packaging goals for HB LEDs.

certain angle. Total internal reflection is the most significant barrier in extracting the light from an LED chip.

To manufacture white HB LEDs, manufacturers cover blue LEDs with a phosphor that emits light in the white region when it irradiates with blue light. Developing the phosphor that most efficiently converts blue light to white is part of the IP (intellectual property) of some LED vendors that purchase LED chips from other vendors and then package them with their own phosphor mixture in a package. Because of the LED chips' high index of refraction, the package needs a transition layer between the air and the chip/phosphor combination. This layer also serves as a protectant and a lens. Low-power indicator LEDs use an epoxy encapsulant, but epoxy tends to yellow when you expose it to high heat and

Figure 2 The Lumex HB SuperBeam LED uses an internal primary optical reflector to direct edge-emitted light from the die out the top of the package.

UV (ultraviolet) radiation, according to Kee Yean Ng, product-marketing manager for solid-state lighting and displays in Avago's optoelectronics-products division. "Silicone is now almost universal as both the lens and the encapsulant for HB-LED packages," he says. The silicone helps both to extract the light and to protect the chip from air and moisture.

Some HB LEDs are surface-emitting, meaning that most of the light comes from the top surface of the die. However, many HB LEDs, especially those that HB-LED packagers purchase, are edgeemitting, and the package must redirect the light so that it exits the top of the package. Several proprietary methods exist for redirecting edge-emitted light. One method is surface roughening, which is a secondary manufacturing process that roughens the surface to make it less reflective to the internal light. Lumex uses primary optics—those that are part of the HB-LED package—that redirect the light from the top in a pinpoint pattern (Figure 2).

Most of the electron-hole combinations that don't result in photons create heat—the biggest drawback to LED life. LEDs generate less light as they get hotter. In addition, all manufacturers specify and test their LEDs at room temperature with a test pulse rather than a continuous current, so the LED never heats up. In practice, however, an LED's junction temperature is never at room temperature when the LED is on. Thermal performance also affects LED lifetime: The hotter the junction temperature, the shorter the LED lifetime will be. Cooler LEDs lose less light due to thermal inefficiency, have a more efficient light output, and last longer.

You can compare the thermal performance of various LEDs by looking at the thermal-resistance rating. The lower it is, the less temperature difference there will be between the junction and the solder point. The thermal path for any LED system starts at the solder point and includes the case temperature of the LED out to the ambient temperature, the PCB (printed-circuit board) that it's mounted on, and its thermal-interface material. These thermal-design steps are the same ones engineers use to determine the operating points for power MOSFETs. Even though you can't measure the junction temperature of the LED chip, you can measure the solder-point temperature to

determine the power going through the LED and use it to calculate the junction temperature. The junction temperature is useful for understanding lumen maintenance, or how long you can expect the LED to remain operational at its operating temperature.

Lumen maintenance is the percentage of initial light output an LED can maintain over its operational life. The predominant failure mode of an LED is to get dimmer over time rather than to burn out as an incandescent bulb does. Lumen maintenance is an agreed-upon number that defines end of life for an LED and generally is L70, which means that the LED is emitting 70% of the light it did at its maximum output when it was new. Energy Star requirements for solid-state lighting set the lifetime at L70, as well. "We've done a lot of higher-temperature testing and found out that the primary mode of degradation for HB LEDs is the package itself," says Paul Scheidt, product-marketing manager at Cree. "If you keep the package cool, the chip doesn't degrade all that much over time—maybe 2 to 3% not that much of a contributor compared with a total 30% degradation over years." The predominant failure mode is due to degradation of the materials, including silicone and plastic, in the package. Both deteriorate over time in different amounts at different temperatures and light intensities.

The question of aging, reliability, and lifetime for LEDs is not a simple one: High-power LEDs have not been in existence long enough to have lifetesting numbers. A common number for LED life is 50,000 hours, or almost six years, which is longer than the most recently introduced high-power LEDs and their packages have existed. But how useful is it to know that an LED has a 50,000-hour lifetime if a manufacturer measured that lifetime in an environment that differs from the one in which your application must operate? For example, a flashlight may require a lifetime of only 1000 to 2000

+ For links to the Web sites of companies this article mentions, go to www.edn.com/100107df.

+ For more technical articles, go to www.edn.com/features.

hours. Users who don't need the full 50,000 hours want to know how to calculate lifetime numbers under different operating conditions. "We have what we call the four critical parameters: junction temperature, drive current, solder-point temperature, and ambient temperature," says Scheidt. "Knowing these parameters, users can get a good estimate of how long the lifetime is going to be, not just of whether they're going to achieve 50,000 hours."EDN

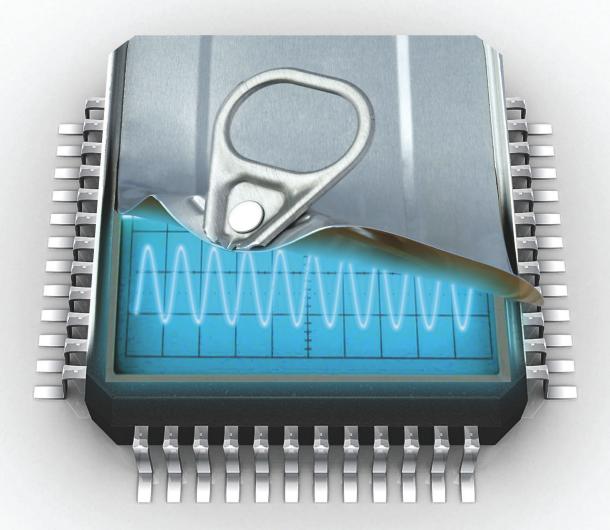

## **UNDER THE LID**

## ANALOG TEST IS SUDDENLY THE CRITICAL INGREDIENT

AFTER YEARS OF ATTENTION TO DIGITAL-TEST TECHNOLOGY, ANALOG TEST IS EMERGING AS A ROADBLOCK TO COST REDUCTION.

TPG (automatic-test-pattern generation), BIST (built-in self-test), and structural-test techniques have kept digital-test costs nearly constant during the explosion in digital complexity. Without these tools, however, as analog complexity starts to grow rapidly, analog-test cost is growing, too. "AMS [analog and mixed-signal] circuits account for 70% of SOC [system-on-chip]-test cost and 45% of test-development time, even though they make up a small fraction of the chip complexity," said Karim Arabi, senior director of

at the ITC (International Test Conference) in Austin, TX, last November. "There is no ATPG for AMS circuits. There is no practical fault model. And what DFT [design-for-test] and BIST efforts we use are purely custom." Arabi's complaint neatly summarizes the situation.

engineering at Qualcomm, speaking at a panel on analog-IC test

Three broad strategies for analog test now exist. The first and most traditional approach is characterization—sweeping the inputs through their full allowable range and measuring all the pins to verify each parameter on the data sheet. This approach still dominates—for good reason—in the world of discrete analog components. The second approach, increasingly common in the SOC world, is to use hardware in the chip itself to test the AMS circuitry. The ideal of this school is to achieve something like BIST for AMS: functional blocks that test themselves on command. The third approach is the Holy Grail of AMS test: structural test.

"We need to redefine the problem," said Craig Force, a test-engineering-platform manager at Texas Instruments, speaking to his fellow ITC panelists. "We don't want to do parametric test of everything on the data sheet. We want to do the minimum number of tests to prove that the circuit is built right." Despite years of effort, the goal remains elusive, but hope seems to be rekindling among some experts.

## **PROVING THE DATA SHEET**

"In our world, we are always fighting for dc precision and for signal fidelity," says Michael Purtell, product- and test-engineering manager at analog-components vendor Intersil. "You are always asking yourself if you are measuring the part or the equipment. For instance, you look at a spectrum going through an analog-to-digital conversion. What part of what you see is really the device, and what part is due to your measuring technique?"

Welcome to the world of precision analog components, in which the claims on the data sheet define the functional requirements. Because the manufacturer doesn't know how a customer will use the chip, there is no choice but to verify every number on the data sheet. "We test the minimum/maximum numbers 100%," Purtell says. "If something is untestable, we will write it up on the data sheet as 'typical." Such thoroughness leads to long, complex test routines on expensive analog testers with elaborate load boards. Fortunately, however, there is no internal state—at least in purely linear circuits—and it is often suffi-

cient to examine just the pins of a device. "Usually, once you set up the configuration registers for a test mode, you can figure out what you need to know from just the inputs and outputs," Purtell says.

Such exhaustive testing is not always necessary. "Different markets have different test needs," says Mark Hemming, director of product development at audio-chip vendor Nuvoton. "An automotive customer can be demanding and insist that your test procedure cover everything on the data sheet. For the same part, a commercial customer might just want you to check that the chip works."

## THE SOC SIMPLIFICATION

Although discrete analog components often require full testing of data-sheet parameters, AMS IP (intellectual-property) blocks in SOCs benefit from a defined environment and usually a fixed set of functions. These constraints reduce the test challenge from full characterization to simply verifying some functions. The almost-ideal case is an IP block that implements a standard interface for which the standard defines the test requirements.

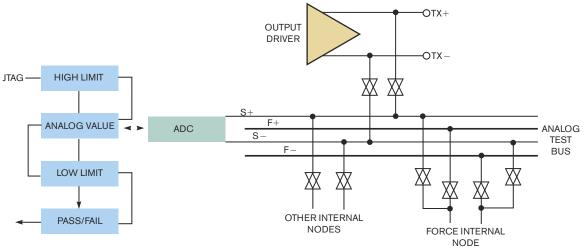

Another considerable simplification for SOC designers is the availability of lots of digital logic. Virtually free gates make it easy to build mode-control registers and to digitally configure the AMS block for test modes: Shorting inputs and enabling loop-back paths are both examples of test modes. The digital wealth also makes possible the latest trend in SOC test: on-chip instrumentation. "We are deep in the throes of on-chip instrumentation," Force says. "Everyone puts a widget in their SOC."

The trend has gathered the most momentum in digital blocks in which, Force says, off-the-shelf IP often implements test functions. In more purely linear blocks, test instruments tend to be ad hoc designs. Instruments for each design incur additional design time and die area. These costs don't mean you can't build a signal generator, a voltmeter, and an oscilloscope into your SOC. They do mean that you must do as much of the work as possible in the digital domain and reuse test circuitry for other purposes.

"In an SOC there's a high comfort level with handling digital signals," Force says. "Digital is a great medium for passing around data, so anything we can

## AT A GLANCE

- Test cost for analog circuits is now significant.

- ☑ Traditional techniques may be inappropriate for analog IP (intellectual property) in SOCs (systems on chips).

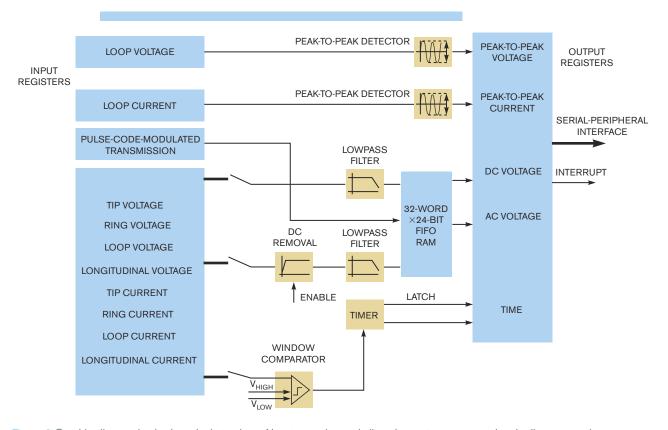

- On-chip instruments and test buses are now in wide use.